日本東大教授提出 8nm NAND Flash 的可能解決方案

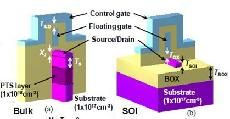

上個月在大阪舉辦的 SSDM 2011 大會上(Solid State Devices and Materials),日本東大的竹內建教授提出使用旺宏的 3D NAND Flash 技術 + SOI 技術,可以把 NAND Flash 的製程一口氣再微縮到8nm。以往的 Floating Gate Cell 技術理論值只能到 8nm ,因為會有量子效應的干擾問題,透過旺宏與竹內建教授所提出的這個技術,可以增加單一空間 NAND Flash 的密度,故能達到 8nm 的目標,製程的再精進,可以讓 SSD 的容量更往前躍進,間接幫助 SSD 的普及化。

雖然目前還是紙上談兵,但是畢竟是前進了一大步,不是嗎?

編按:這是 VIP 網友 ACGFAN 的第三篇貢獻[責任編輯:Sagat.Y]